Inicio Unidad I Unidad II Unidad III Unidad IV Unidad V Bibliografía

Un conversor analógico-digital es un dispositivo electrónico que convierte una señal analógica de voltaje a un número digital. La salida digital puede usar diferentes esquemas de codificación, como binario o BCD.

En esta definición están presentes los cuatro procesos que intervienen en la conversión analógica-digital:

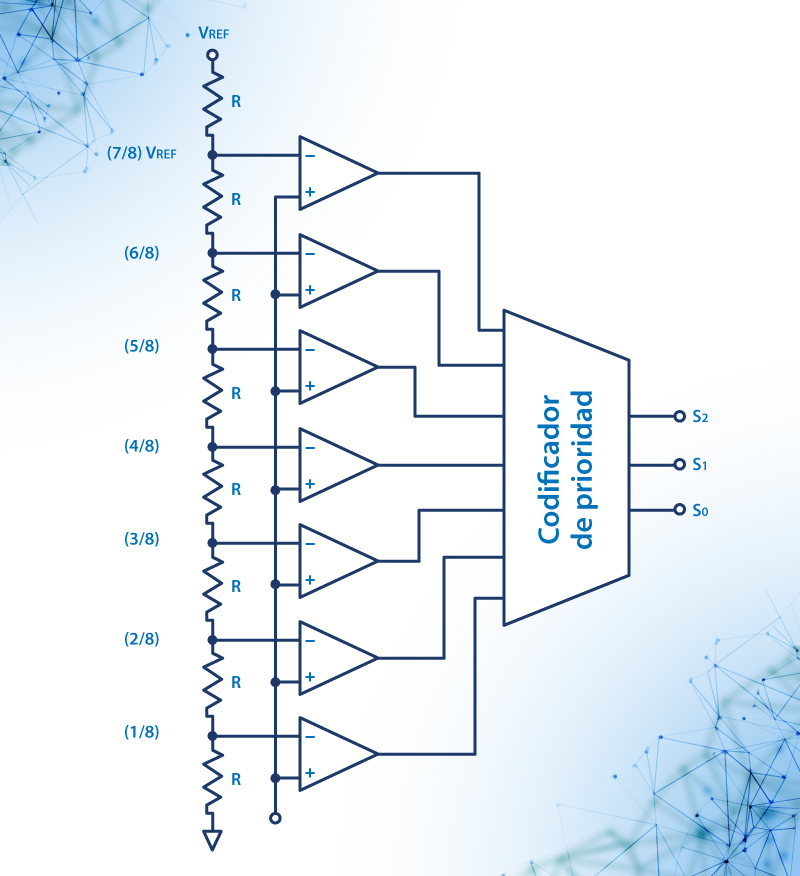

CAD tipo PARALELO o FLASH

Este codificador es un dispositivo combinacional con n entradas y salidas, tal que, en un instante cualquiera, sólo una entrada toma el valor 1, para la que el circuito genere su código digital de salida.

Los codificadores de prioridad prevén la posibilidad de que más de una entrada o tecla de activación están activas simultáneamente. Generalmente el circuito decide entre dos entradas simultáneas escogiendo la mayor de ellas.

Este convertidor es muy rápido, ya que la conversión se realiza de forma simultánea y casi instantánea. El tiempo de conversión viene determinado por la velocidad de los comparadores y el codificador.

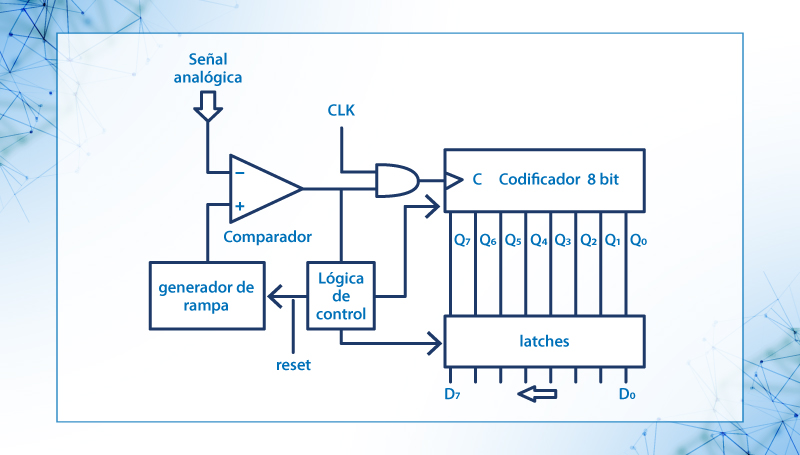

Entre el codificador de prioridad y los comparadores suele intercalarse un registro (puede ser de biestables D) cuando la entrada varía rápidamente.

El reloj es el que controla la transferencia de datos a través de los registros.

Figura 92. Esquema ADC tipo paralelo o flash.

Estos CAD suelen denominarse de tipo “flash”, por la velocidad que suelen alcanzar, hasta cientos de MHz los más rápidos actualmente.

En los modelos comerciales, la salida de cada uno de los comparadores se almacena en un circuito de cerrojos (“latches”), antes de pasar al codificador de prioridad.

La adición de un bit duplica aproximadamente el número de comparadores. Además, el número de puertas que requiere la lógica digital aumenta con el número de comparadores en un orden logarítmico al número de comparadores. En consecuencia, estos modelos se emplean sólo en aplicaciones que requieran alta velocidad.

El conversor flash está constituido por una serie de comparadores analógicos que comparan voltajes de referencia con el voltaje de entrada analógico. Cuando éste excede el voltaje de referencia para un comparador, se genera un valor alto.

En este conversor para la conversión de un código binario a n bits a se necesita n comparadores.

El voltaje de referencia se establece para cada comparar por medio de la red divisora de voltaje resistiva. La salida de los comparadores se conectará a una entrada del codificador de prioridad.

Ventajas

Desventajas

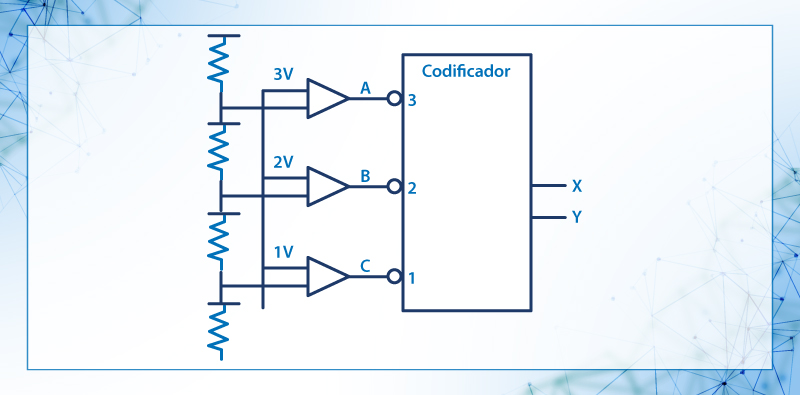

Ejemplo 11.-¿Cuál es la tabla de verdad para el siguiente circuito ADC flash?

Figura 93. Circuito para el ejemplo 11.

Solución:

Va es el voltaje de entrada, ABC son los comparadores que generarán las salidas de 1 o 0 dependiendo del valor Va de entrada, XY es el resultado digital. El codificador trabaja con entradas en bajo, por lo que cuando recibe alguna de estas genera la salida correspondiente al valor de entrada.

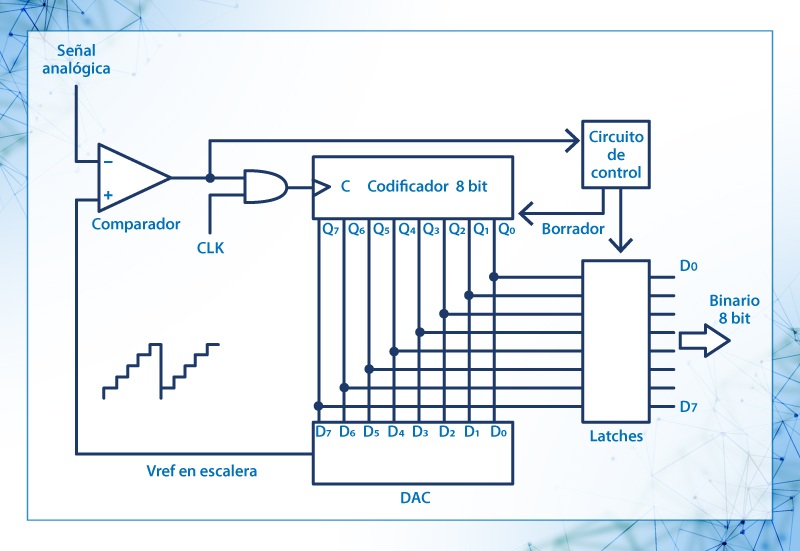

CAD de RAMPA en escalera

Una de las versiones más simples del convertidor AD hace uso de un contador binario cómo registro y permite que el cronómetro incremente un paso a la vez hasta que Vr ≥ Ve. A este se lo llama convertidor A/D con rampa digital ya que la forma de onda en Vref es una rampa que funciona paso por paso (en realidad es escalón por escalón).

Figura 94. ADC de rampa en escalera

La señal de entrada Ve se compara con la señal del convertidor Vr, cuando ambas son cero el dispositivo está en reset, al entrar Ve mayor de cero, pero menor que Vr, se produce un pulso de inicio en el contador y en el generador de rampa, a continuación el amOp compara el valor de Ve con el valor de la rampa Vr, cuando el valor Vr ≥ Ve se genera un pulso , el contador se detiene, reseteándose el sistema. El contador mantendrá el valor hasta que una nueva conversión de inicio nuevamente.

Ejemplo 12.-Utilizando el método rampa en escalera calcular el % de resolución y el valor digital que se obtiene si el voltaje de entrada=5V, el valor Vt=2 mV, el valor total de salida=13V y maneja 6 bits.

Solución:

I) Para calcular el valor digital equivalente al voltaje de entrada Va=5V, es necesario conocer el tamaño del paso, es decir el valor de los incrementos que tendrá para llegar al valor máximo. Para eso se calcula la cantidad total de pasos que puede llegar a realizar --> 2⁶-1=63. Teniendo este valor se calcula el tamaño del paso que es: [V total de salida/cantidad de pasos]= 13V/63= 0.206V.

Una vez que se obtuvo el valor anterior se calcula el número de pasos, para esto se divide Va/tamaño del paso=5V/0.206mV=24.27 ~~ 25 pasos, por lo que obteniendo el valor binario de la cantidad que se acaba de obtener resulta el equivalente a la entrada Va=5V.

2510 =011001.

II) Para el cálculo del porcentaje de resolución se aplica la siguiente fórmula (1/cantidad de pasos)*100

Sustituyendo: (1/63)*100=1.58%

CAD de SEGUIMIENTO o RASTREO

Es más rápido que el método de rampa, ya que el contador no se restablece después de cada muestra. Se utiliza un contador ascendente –descendente el cual cambia su estado dependiendo de cuando el valor de Vr sea > o < que el voltaje de entrada Ve. De esta manera el contador siempre hará su cuenta en el sentido del voltaje de entrada

Consulta la bibliografía y dibuja el esquema del ADC de seguimiento o rastreo

CAD de APROXIMACIONES SUCESIVAS

Un circuito similar al utilizado en los conversores de seguimiento, pero ahora, cada vez que se realiza una conversión se ensayan los sucesivos bits empezando por el más significativo. Según se obtenga un valor menor o mayor se añade o no el bit al control del conversor digital analógico. El tiempo necesario (número de pulsos de reloj) es siempre igual al número de bits más uno.

Para evitar que la señal de entrada varíe durante la conversión (unos pocos microsegundos) se utilizan circuitos de muestreo y retención (Sample & Hold) o cuando el espectro de la señal de entrada lo permite un simple filtro pasa bajos que limite la velocidad de variación de la señal por debajo de 1 bit menos significativo en el tiempo que dura una conversión

La rapidez, precisión y estabilidad de los conversores de aproximación sucesiva hace que estos sean los más utilizados en la gama de 8 a 16 bits y velocidades entre 10Hz y 1MHz. A velocidades menores se utilizan conversores de doble rampa y a mayores, conversores de tipo flash.

Ejemplo 13.-Calcula la resolución para un circuito de aproximaciones sucesivas que a la salida tiene un tamaño de paso de 176, trabaja a 9 bits y a la entrada hay 5 V.

Solución

Para calcular la resolución teniendo estos datos se aplica la siguiente formula: entrada/paso=resolución

por lo que: 5/176=0.028V=28 mV.

Ejemplo 14.-Realiza los cálculos necesarios, demuestra qué método es más rápido al realizar la conversión, escalera vs aproximaciones sucesivas, si se tienen valores de 7 bits para cada uno y trabajan a 2,000,000 Hz.

Solución

Conociendo la cantidad de bits y la frecuencia a la que trabajan es suficiente para calcular el tiempo en ambos circuitos.

Como la frecuencia está en hz será más conveniente hacer una conversión a Mhz para obtener el resultado en 1/seg, por lo que: 1 Mhz=1,000,000 hz --> 2,000,000/ 1,000,000=2Mhz.

Ahora se aplica la fórmula para calcular el tiempo de conversión de un ADC de escalera:

(2n-1)(frec. de reloj)= (27-1)(0.5)=1/32 seg.

La fórmula para el ADC de aproximaciones es: (N bits*frec. de reloj)= (7)*(0.5)= 1/3.5 seg.

Nota: se multiplica por 0.5 en lugar de multiplicarse por 2 ya que a mayor velocidad, se reduce el tiempo de respuesta.

Consulta la bibliografía y dibuja el esquema del ADC de seguimiento o rastreo.

CAD de PENDIENTE SIMPLE Y DOBLE

CAD de pendiente simple

Este tipo de convertidores no utilizan convertidores CDA. Se utiliza un generador de rampa lineal de pendiente constante.

Figura 95. Esquema del ADC de pendiente simple

Al inicio el amplificador operacional en modo comparador tiene ambas entradas en cero, al entrar la señal analógica el comparador produce un nivel alto en la salida, esto habilita la señal de reloj para el contador y arranca el generador de rampa. Suponiendo que la entrada es de valor Ve el generador de rampa alcanza este valor, produciendo la salida de cero en el comparador, esto resetea el contador y al mismo tiempo guarda el valor de la cuenta binaria, en los latches de salida mediante la lógica de control.

La cuenta habrá contado hasta alcanzar el valor de Ve, Dicho en otra forma, cada vez que se alcanza el voltaje de entrada por el voltaje de rampa, se produce una lectura binaria que puede ser fácilmente cambiada a dígitos decimales.

Este tipo de convertidor de pendiente simple se usa frecuentemente en los voltímetros digitales.

Ejemplo 15.-Un convertidor analógico digital de tipo pendiente simple tiene una entrada analógica de 5 V, si termina la conversión utilizando una frecuencia de reloj de 500 kHz y la rampa se incrementa en 1 V/ms. ¿Cuántos pulsos habrá generado el reloj cuando se realice la conversión?

solución

Como el valor de la rampa se incrementa 1 volt cada milisegundo, para alcanzar los 5 V de la entrada analógica, entonces tardaría 5 milisegundos en realizar la conversión.

Para calcular el número de pulsos se multiplica la frecuencia por el tiempo --> 500(5)=2500 pulsos

CAD de pendiente doble

Este convertidor usa dos generador uno de rampa variable y otro de rampa constante esto se logra con el empleo de un amplificador operacional en modo integrador.

En estado inicial se aplica un voltaje Ve lo cual provoca que se cargue el capacitor C a través de R a un voltaje proporcional al Ve puesto que R se encuentra conectado a la a tierra virtual de la entrada inversora del amp-OP. En seguida La Lógica de control cambia Sw a –Vref , provocando que el capacitor se descargue en un tiempo proporcional al valor del Ve, al producirse una pendiente negativa de valor constante, al mismo tiempo arrancando el contador y terminando la cuenta de este, alcanzándose una cuenta proporcional al valor de entrada de VE, esta cuenta se almacena en los latches, produciéndose así un ciclo de medición. Este método de CAD de doble rampa se usa frecuentemente en los multímetros digitales.

Consultar la bibliografía y dibujar el esquema del ADC de pendiente doble