Inicio Unidad I Unidad II Unidad III Unidad IV Unidad V Bibliografía

En la actualidad existen circuitos que se pueden programar para obtener funciones digitales diversas mediante un proceso de programación, llamados PLD (Programmable Array Logic), el uso de estos PLD, permite reducir considerablemente el número de circuitos requeridos para implementar una función lógica.

Existen en el mercado varios tipos de PLD como son:

Una característica relevante de los sistemas digitales es su capacidad de almacenar una gran cantidad de datos en forma temporal o permanente, esto permite realizar las operaciones que se realizan por ejemplo en las computadoras, entre otras aplicaciones diversas.

Memorias ROM o memorias de sólo lectura.

Estas memorias ROM son de diferentes tipos los, que se diferencian por la forma de ser programados y borrados:

A medida que aumenta la facilidad de borrado y programación aumenta el costo y tiempo de acceso a los datos, pudiendo ser esto una característica para la decisión de la selección para su aplicación .

Investiga los campos de aplicación de las memorias ROM en sus diversos tipos

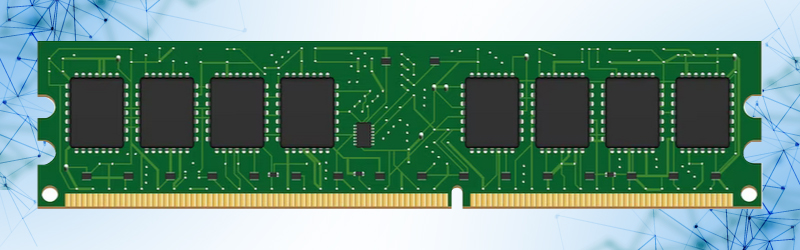

Memoria RAM

El acrónimo RAM significa acceso aleatorio, es decir cualquier posición de memoria es tan accesible como otra, esta memoria tiene la ventaja de ser de gran capacidad y consumir menor energía que una memoria ROM, pero no es de almacenamiento permanente, esto significa que al quitarse la alimentación eléctrica se pierde la información.

Es muy usada en sistemas de cómputo para almacenamiento temporal de programas y datos.

Figura 76. Memoria RAM

Memoria RAM estática (SRAM).

Esta memoria está construida en esencia a base de Flip-flops con tecnología CMOS de tipo BiCMOS y NMOS, la primera a base de transistores y la segunda con MOSFET

Ambas tecnologías han evolucionado considerablemente, en la actualidad se tienen memorias de gran capacidad y velocidad, este tipo de memoria es capaz de almacenar los datos indefinidamente hasta que se pierda la energía de alimentación.

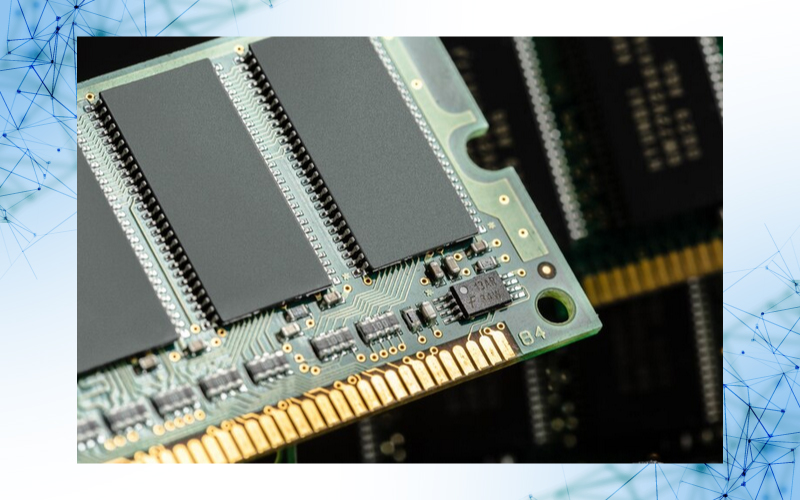

Memoria RAM dinámica (DRAM)

Las memorias DRAM son construidas en base a pequeños capacitores para almacenar la información ,1 y 0 cargado o no el capacitor, son de una gran capacidad de almacenamiento y poco consumo de energía, pero tiene la desventaja que los capacitores tienden a descargarse, por lo que requieren circuitos de recarga o también llamados de refresco de datos. Pero son usadas preferentemente cuando se requiere menor costo y menor potencia.

Figura 77. Memoria RAM estática

Ejemplo 9.-Describe memoria DRAM y SRAM para laptop

Estos dos tipos de memorias son como ya se dijo, de acceso aleatorio, se utilizan en la memoria de las computadoras y laptops, en ellas se guardan los datos que se están operando, ya sea para almacenar temporalmente o para tener los datos en forma inmediata para hacer operaciones que se puedan realizar en forma inmediata por la CPU.

Ambas tienen ventajas y desventajas, la SRAM son memorias más rápidas que las DRAM pero tienen menor capacidad de almacenamiento, se usan preferentemente en memorias tipo caché. Las memorias DRAM son de mayor capacidad y menor costo, se utilizan como memoria principal.

La DRAM se diseñó para superar las desventajas de la SDRAM; se redujo su costo y aumentó la capacidad de almacenamiento, pero es más lenta y de mayor consumo de energía.

Investiga cuales son las memorias empleadas en las computadoras tipo Laptop; Marcas, su nomenclatura, su capacidad y costos.

El diseño con PLD’s tiene las siguientes ventajas en relación a la lógica cableada:

Los circuitos programables PLD, (Programable Array Device), son todos los dispositivos programables, de acuerdo a sus características se dividen en ROM, PLA y GAL, en el apartado anterior se trataron los tipos de ROM, en seguida veremos los PLA y GAL

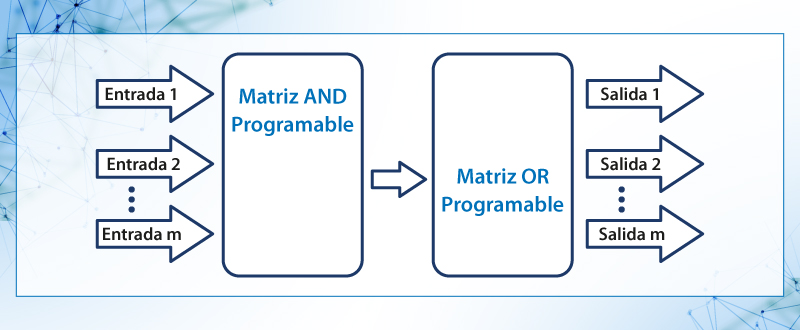

Circuitos PLA

(PLA, Programmable Logic Array)

El PLA es un PLD formado por una matriz AND programable y una matriz OR programable. La PLA ha sido desarrollada para superar algunas de las limitaciones de las memorias PROM. Tienen ambos planos programables, esto hace que su costo se eleve y sea su desventaja.

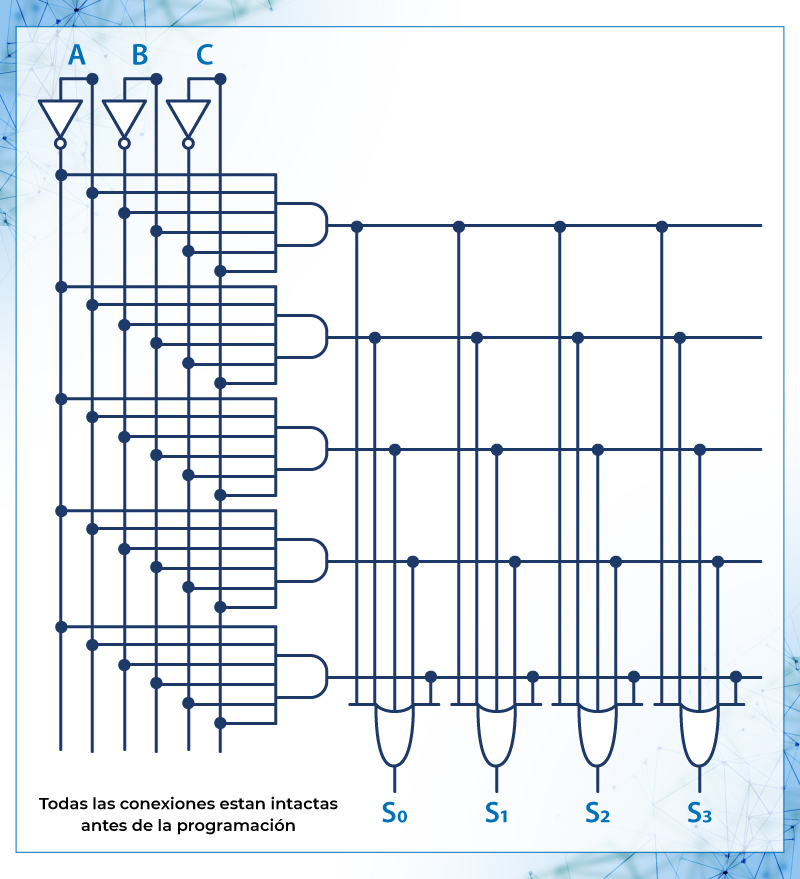

Figura 78. Diagrama de circuito programable PLA

Estos dispositivos contienen ambos términos AND y OR programables lo que permite a cualquier término AND alimentar cualquier término OR. Las PAL probablemente tienen la mayor flexibilidad frente a otros dispositivos con respecto a la lógica funcional. Normalmente poseen realimentación desde la matriz OR hacia la matriz AND que puede usarse para implementar máquinas de estado asíncronas.

La mayoría de las máquinas de estado, sin embargo, se implementan como máquinas síncronas. Con esta perspectiva, los fabricantes crearon un tipo de PLA denominado Secuencial (Sequencer) que posee registros de realimentación desde la salida de la matriz OR hacia la matriz AND.

¿Qué es?

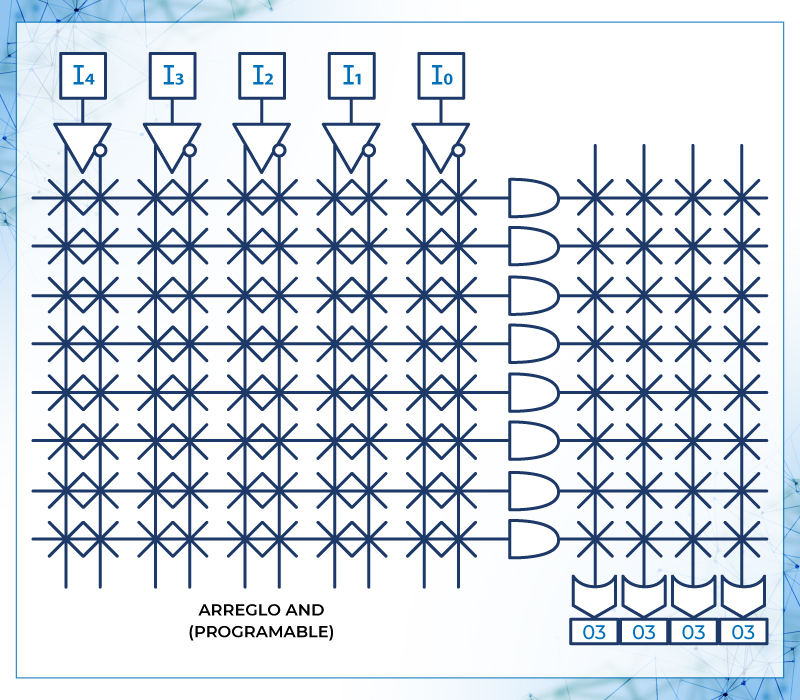

Figura 79. Diagrama esquemático de un CI PLD programable

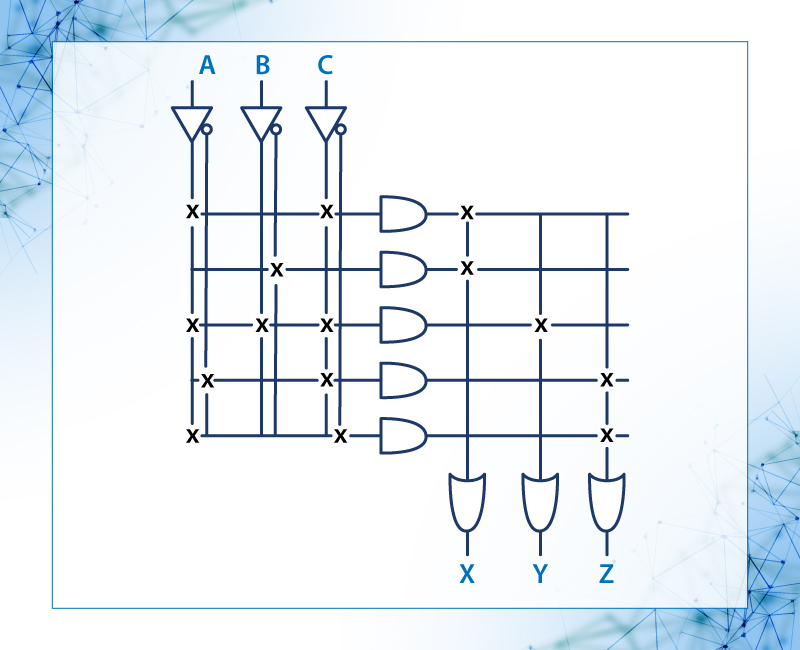

Figura 80. PLA 3x4 con 5 términos producto

Ejemplo 10.-Reduce a la mínima expresión los minitérminos y muestra el esquema de la PAL programada.

Solución

Ecuaciones

X= AC+B’

Y= ABC

Z= A’C+AC’

Figura 81. Esquema de la PLA programada

GAL

Otro tipo de PLD son las GAL

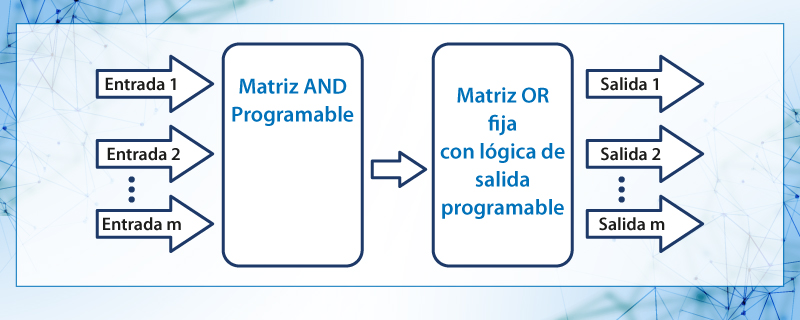

Las GAL son dispositivos de matriz lógica genérica. Esto tiene entradas AND programables, una matriz OR fija y una salida lógica programable. Están diseñados para emular muchas PAL.

Figura 82. Diagrama de circuito programable PLA

Método de programación de dispositivos.

Cabe mencionar que no es propósito de esta unidad el mostrar cómo se programan los PLD, ya que esto se hace en la UAP de Dispositivos Programables

Pero sí señalaremos lo siguiente:

El proceso de diseño lógico con PLD’s se resume en tres grandes etapas:

Diseño lógico

Dentro de la primera etapa, los pasos involucrados son los mismos que en cualquier diseño digital, combinatorio o secuencial, y se pueden subdividir en los pasos siguientes:

Implementación

La implementación del diseño consiste en seleccionar y usar las herramientas, tanto de hardware y software, necesarias para la traducción de los resultados a un mapa de fusibles para la programación del chip. Esta fase consiste en:

Verificación

La etapa final consiste en la verificación del diseño en la cual la correcta programación del PLD es comprobada, por medio de técnicas de simulación

Los pasos de la verificación son:

Ejemplo 11.-Ejemplo de circuito GAL que existen en el mercado

El GAL es un tipo de circuito integrado de marca registrada por Laticce Semiconductor diseñada para sustituir a la mayoría de las PAL, teniendo compatibilidad con sus terminales.

Entre los principales fabricantes están: Laticce, Philips, Texas Instruments, entre otros.

En la página web http://pdf1.alldatasheet.com/datasheet-pdf/view/70208/LATTICE/GAL22V10D-10LJ.html se pueden observar las características del a GAL 22V10, que es un circuito que permite 22 entradas y 10 salidas.

Muestra tres ejemplos de PLA y tres ejemplos de GAL comerciales, señalando su capacidad y costo.

Programador universal

Para programar los PLA o GAL se usa un dispositivo llamado programador de PLD, el cual se alimenta con un programa . jedec que se genera a través de un lenguajes de programación de PLD s especifico, como OPAL ( Open Programable Architecture Languajes), Lenguaje Abierto de Arquitecturas Programables

En este lenguaje, se ofrece al diseñador usar lenguaje de máquinas de estado, ecuaciones booleanas multi-nivel, así como funciones de tabla de verdad, etc. Esto le proporciona libertad para seleccionar la implementación que mejor se adapte a las especificaciones del diseño.

Como ya se mencionó no es propósito de esta unidad el mostrar cómo se programan los PLD, ya que esto se hace en la UAP de Dispositivos Programables

Solamente se muestra un ejemplo de aplicación resuelto con un lenguaje OPAL.

Ejemplo 12.-Diseña un convertidor de un número binario de 4 bits a una salida ASCII de 7 bits utilizando tablas de verdad, mostrando solamente el implementar un vector de prueba en un dispositivo PAL16L8.

Solución

El listado a cargar en el editor del OPAL es:

BEGIN HEADER

Este es un convertidor de 4 bits a una salida en c¢digo ASCII de 7 bits,

utilizando tablas de verdad.

END HEADER

BEGIN DEFINITION

DEVICE p16l8;

INPUTS w=1,x=2,y=3,z=4;

OUTPUTS (COM) /a6=12,/a5=13,/a4=14,/a3=15,/a2=16,/a1=17,/a0=18;

END DEFINITION

BEGIN TRUTH_TABLE

TTIN w,x,y,z;

TTOUT /a6,/a5,/a4,/a3,/a2,/a1,/a0;

0000 0110000

0001 0110001

0010 0110010

0011 0110011

0100 0110100

0101 0110101

0110 0110110

0111 0110111

1000 0111000

1001 0111001

1010 1000001

1011 1000010

1100 1000011

1101 1000100

1110 1000101

1111 1000110

END TRUTH_TABLE

BEGIN VECTOR

w,x,y,z,/a6,/a5,/a4,/a3,/a2,/a1,/a0;

0000 LHHLLLL

0001 LHHLLLH

0010 LHHLLHL

0011 LHHLLHH

0100 LHHLHLL

0101 LHHLHLH

0110 LHHLHHL

0111 LHHLHHH

1000 LHHHLLL

1001 LHHHLLH

1010 HLLLLLH

1011 HLLLLHL

1100 HLLLLHH

1101 HLLLHLL

1110 HLLLHLH

1111 HLLLHHL

END VECTOR