Inicio Unidad I Unidad II Unidad III Unidad IV Unidad V Bibliografía

El modo de empleo lo mostraremos con dos ejemplos

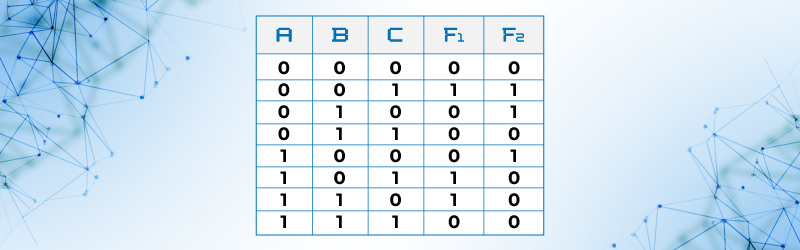

Ejemplo 6.- Diseñar y construir con compuertas digitales el circuito que resuelva la tabla de verdad mostrada en la tabla 31

Tabla 31. Tabla de verdad para el ejemplo 6

Solución:

1.- Obtenemos las funciones con miniterminos, forma canónica:

F1 ={ 1,5,6} F2={1,2,4}

2.- La pasamos a miniterminos

F1 =A’B’C + A’BC + ABC’ F2= A’B’C + A’BC’ + AB’C’

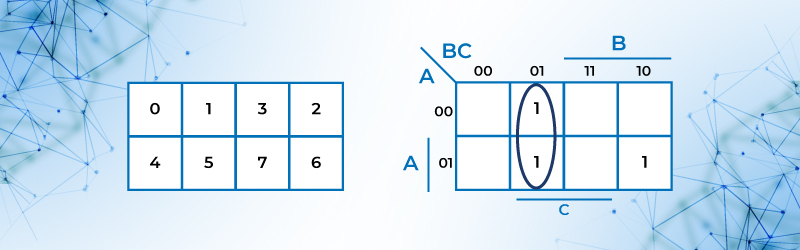

3.- Reducimos por mapas de karnaugh

Figura 42. Mapas de karnaugh

F1 = B’C + ABC’

Para F2 tenemos:

F2= A’B’C + A’BC’ + AB’C’ la cual no se puede reducir

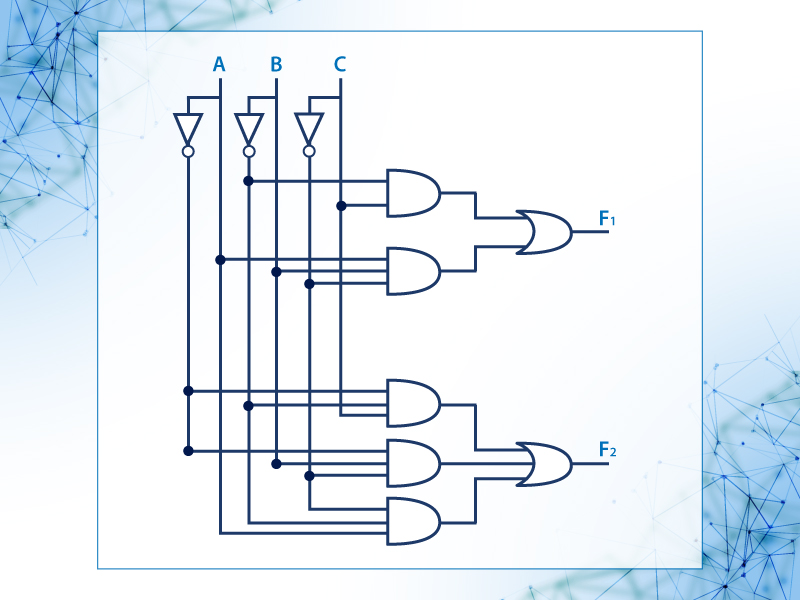

4.- Para construir el circuito se requiere

Para F1 dos compuertas AND de 2 y 3 entradas.

Para F2 tres compuertas AND de 3 entradas cada una

Esto es:

Figura 43. Circuito esquemático con compuertas digitales para F1 y F2

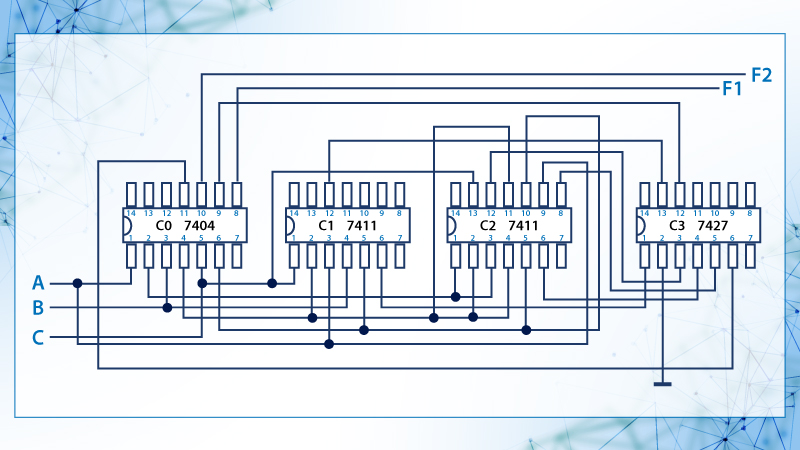

5.- Identificamos los números de las compuertas requeridas, así como sus entradas y salidas

Consultando la bibliografía mencionada anteriormente, requerimos 1 compuerta NOT 7404 con 6 circuitos, 2 compuertas AND 7411 de 3 circuitos con 3 entradas cada una y 1 compuerta OR 7427 de 3 circuitos con 3 entradas cada una.

6.- Quedando el circuito con compuertas como se muestra en figura 65

Figura 44. Circuito con compuertas digitales para F1 y F2

Por que no se puede reducir F2= A’B’C + A’BC’ + AB’C’

Demostrar que el circuito con compuertas de la figura 46 corresponde con la figura 45 circuito digital

Ejemplo 7

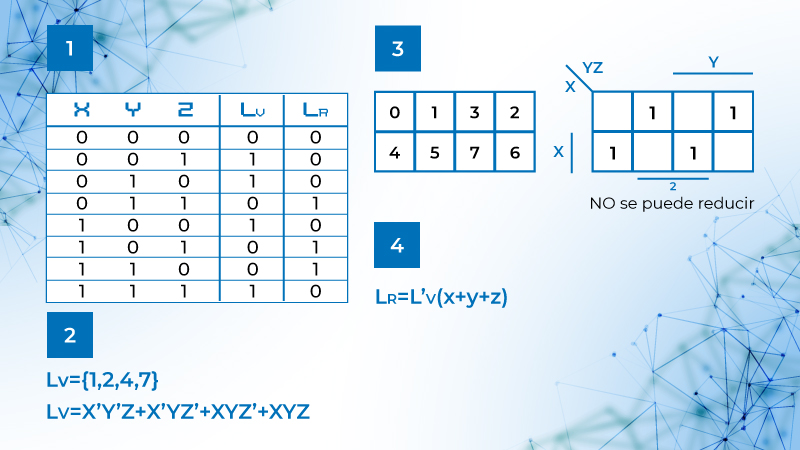

Diseñar y mostrar con compuertas TTL de la serie 74XXX, un circuito digital de TRES entradas X,Y, Z que tiene DOS funciones de salida, Lv y LR de tal manera que si la suma decimal de las entradas es numero NON prende el led verde de Lv y si la suma es par prende el led rojo de LR, y cuando la suma es CERO no prende ningún led.

Solución:

Figura 45. Solución a pasos para LV y LR

5.- Lv = X’Y’Z+X’YZ’+XYZ’+XYZ

LR = L’V (X+Y+Z)

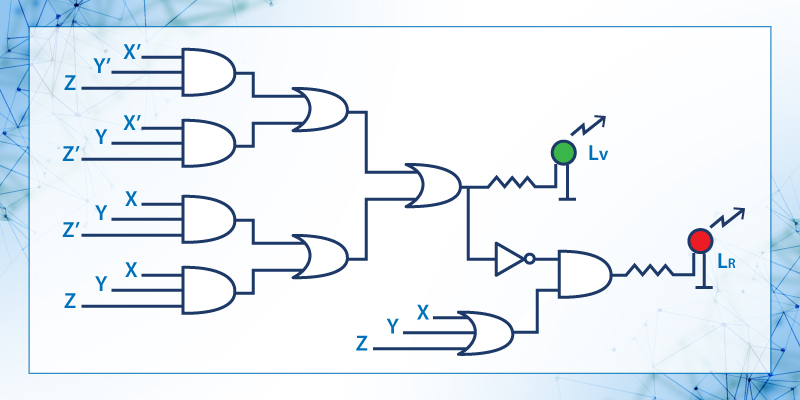

Figura 46. Diagrama lógico digital para LV y LR

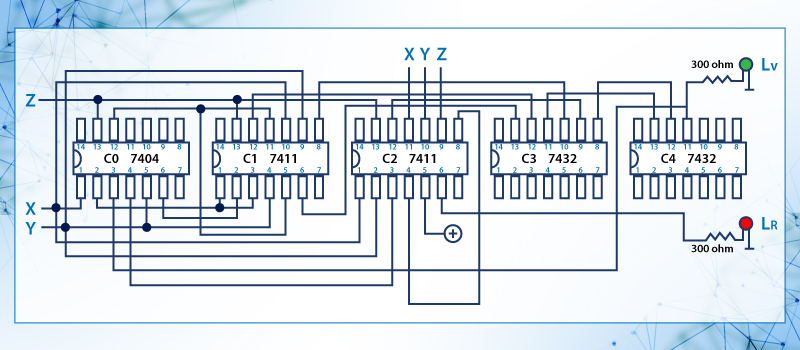

6.- Para realizar el diagrama esquemático con compuertas TTL,,se requieren DOS compuertas AND 7411, DOS compuerta OR 7432, UNA compuerta NOT 7404, DOS resistencias de 300 ohms, DOS leds, uno verde y otro rojo.

Figura 47. Diagrama esquemático con compuertas TTL

Demostrar que el diagrama esquemático con compuertas TTL de la figura 46 corresponde con el de la Figura 47 diagrama lógico digital para LV y LR